在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

1.-invert参数的作用

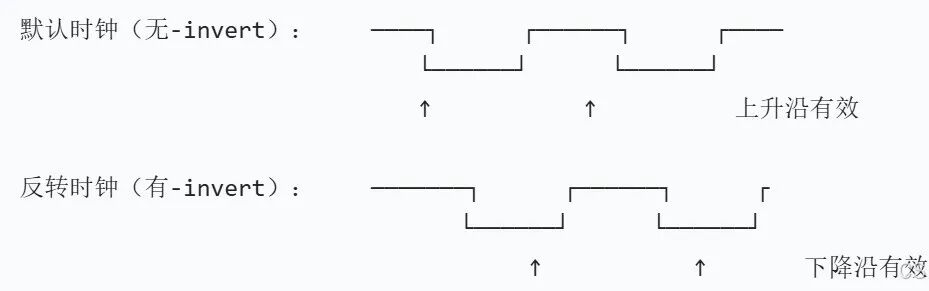

-invert参数的字面含义是 "反转",其核心功能是告诉时序分析工具:信号的有效边沿或逻辑电平与默认状态相反。在数字电路中,信号通常有默认的有效状态(如时钟的上升沿有效、复位信号的低电平有效),而-invert参数允许设计者明确指定信号的实际有效状态,确保时序分析结果与电路实际行为一致。

对于时钟信号,Vivado默认假设上升沿为有效边沿(即信号在上升沿触发寄存器采样)。当使用-invert参数时,表示该时钟信号的下降沿为有效边沿,时序分析工具会基于下降沿计算建立时间(Setup Time)和保持时间(Hold Time)。

对于复位信号或控制信号(如使能信号),-invert参数用于指定信号的有效电平与默认逻辑相反。例如,默认情况下工具可能认为高电平为有效状态,使用-invert后则表示低电平为有效状态。

2.-invert参数的应用场景

-invert参数主要用于以下两类约束命令中,其语法格式和应用场景各有侧重。

1.时钟约束中-invert的典型应用是定义下降沿触发的时钟,语法格式如下:

# 基本语法:创建下降沿有效的时钟create_clock -name-period -waveform { } -invert -ports # 示例:创建一个100MHz(周期10ns)的下降沿有效时钟create_clock -name clk_100mhz -period 10 -waveform {5 10} -invert -ports [get_ports clk_in]

参数说明:

-name:指定时钟名称;

-period:时钟周期(单位:ns);

-waveform:定义时钟波形的上升沿和下降沿时间点(默认 {0 period/2},反转时钟通常设置为 {period/2 period});

-invert:指定时钟下降沿有效;

-ports:指定时钟输入端口。

应用场景:

当电路中存在下降沿触发的寄存器时(如always@(negedgeclk)描述的时序逻辑);

跨时钟域交互中,需要明确区分上升沿和下降沿时钟以避免时序冲突;

双边沿采样电路(如 DDR 存储器接口),需分别约束上升沿和下降沿时钟。

2.延迟约束(如set_max_delay、set_min_delay)中-invert是反转信号的逻辑极性。

# 基本语法:约束反转极性信号的最大延迟 set_max_delay -invert-from -to # 示例:约束低电平有效的复位信号的最大延迟 set_max_delay -invert5-from [get_ports rst_n] -to[get_ pins *reg/R]

参数说明:

-invert:指定信号为低电平有效(默认高电平有效);

-from/-to:指定延迟路径的起点和终点。

应用场景:

低电平有效的复位信号(如rst_n),确保复位信号在低电平时的路径延迟满足要求;

低电平有效的使能信号(如enable_n),约束其有效状态下的路径延迟;

差分信号对中的负向信号(如clk_p和clk_n),明确信号极性以保证时序分析准确性。

3.-invert参数的工程实践

波形设置与-invert的配合:

当使用-invert定义下降沿时钟时,建议将-waveform设置为{period/2 period},使波形描述与实际有效边沿一致:

# 正确:10ns周期的下降沿时钟,波形从5ns开始下降create_clock-name clk_neg -period10-waveform {510} -invert -ports[get_ports clk_in]# 不推荐:波形与-invert含义冲突(仍以0ns为上升沿)create_clock-name clk_neg -period10-waveform {05} -invert -ports[get_ports clk_in]

与时钟分组的协同:

下降沿时钟应单独分组或明确标记,避免与上升沿时钟混淆:

# 将下降沿时钟加入独立时钟组create_clock-name clk_neg -period10-invert -ports[get_ports clk_in]set_clock_groups-name neg_edge_clocks -group[get_clocks clk_neg]

跨时钟域的时序处理:

当下降沿时钟与上升沿时钟交互时,需使用set_clock_uncertainty等约束明确时序关系:

# 为下降沿时钟与上升沿时钟之间的路径设置额外不确定性set_clock_uncertainty0.5-from[get_clocks clk_neg] -to [get_clocks clk_pos]

复位信号的延迟约束:

对于低电平有效的复位信号(rst_n),使用-invert确保工具分析复位有效(低电平)时的路径延迟:

# 约束rst_n(低有效)从输入端口到寄存器复位端的最大延迟 set_max_delay -invert3-from[get_ports rst_n]-to[get_pins *reg/R]# 同时约束最小延迟,避免复位释放时的竞争冒险 set_min_delay -invert0.5-from[get_ports rst_n]-to[get_pins *reg/R]

避免过度约束:

-invert仅需用于实际极性与默认相反的信号,对于高电平有效的信号无需添加,否则会导致时序分析错误:

# 错误:高电平有效信号不应使用-invert set_max_delay -invert2-from[get_ports enable]-to[get_pins *reg/CE]

与多周期路径的配合:

当反转极性的信号涉及多周期路径时,需确保-invert参数与多周期约束协同工作:

# 为低电平有效的控制信号设置2周期路径 set_multicycle_path2-setup -invert -from[get_ports ctrl_n]-to[get_pins data_reg/D]

推荐阅读: